Research Focus

Consideration and Mitigation of Electromigration in Layout Design

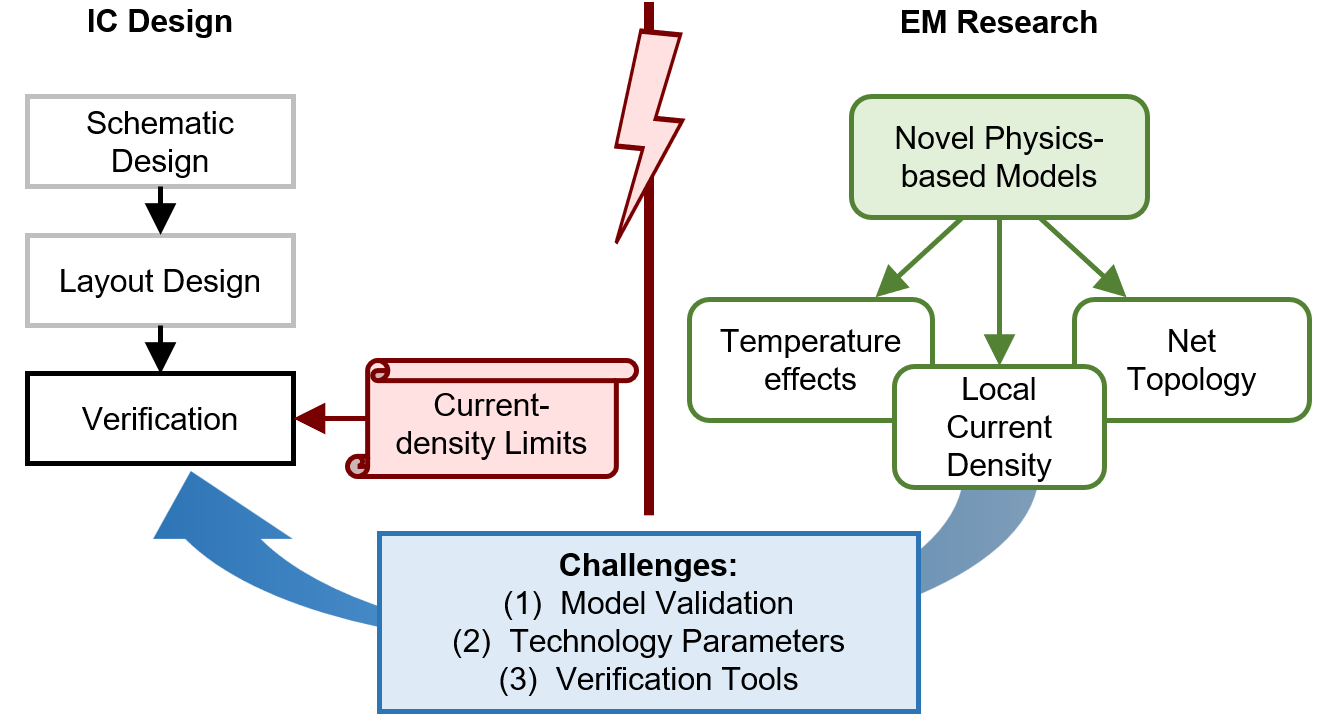

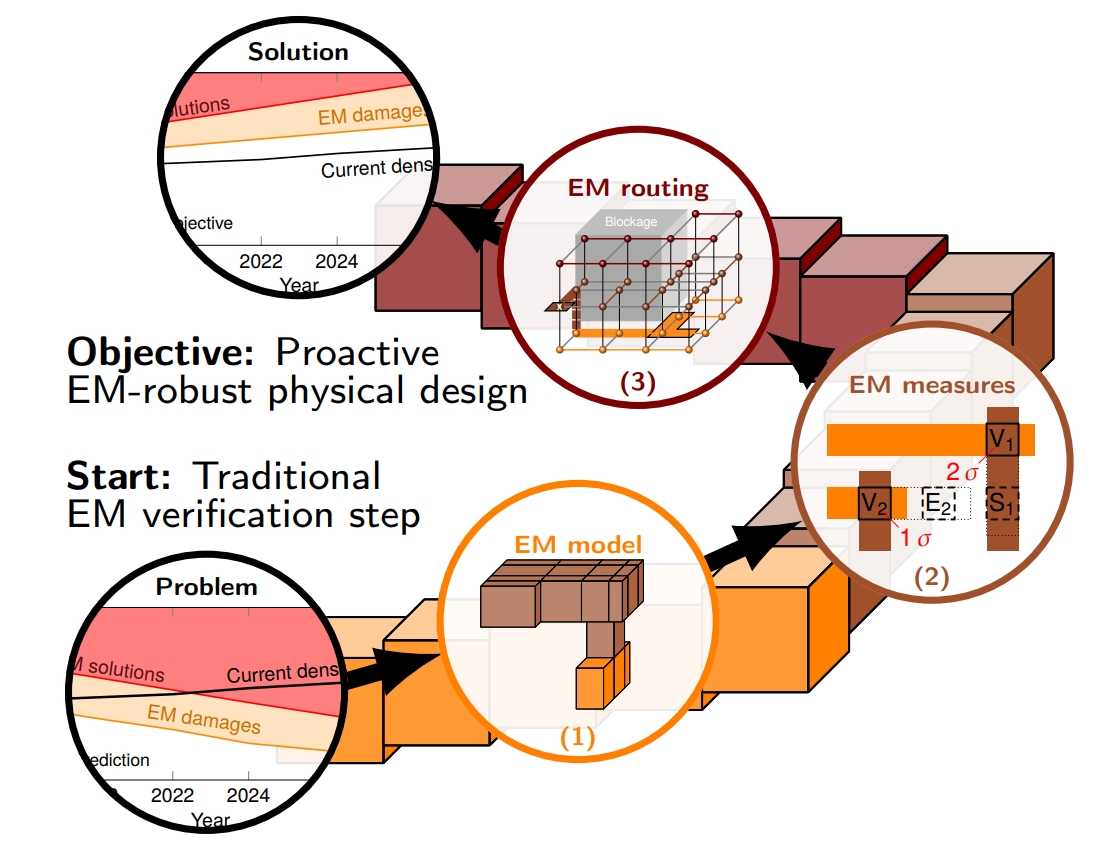

Due to shrinking feature sizes, electromigration (EM) is becoming a growing concern for the reliability of integrated circuits. High current densities cause atom movement within the metal interconnects. This leads to the development of voids that are a typical reason for interconnect failure. State-of-the-art verification methods check a layout design for the maximum allowed current density (und thus its EM robustness). This verification step is conducted after layout synthesis. Yet, this approach is limited by the underlying EM models that only inaccurately capture the physical nature of EM. Therefore, high safety margins must be applied. Moreover, the number of nets affected by EM is continuously rising. The resulting repair effort is getting too high to handle.

In order to enable migration robust IC design in future technologies, we develop methods to enable the practical application of the novel, physics-based stress models for electromigration. These models calculate the stress evolution (as a measure for migration robustness) considering local current density and interconnect topology. Thus, the pessimism inherent to the established current-density verification can be significantly reduced.

Moreover, the IFTE developed and implemented a novel, proactive routing approach that includes migration-robustness constraints already in the routing step. Thus, the repair effort following the verification can be significantly reduced.

Practical applicability of physics-based migration models:

- Development and test of technology characterization procedures for stress modeling - based on standard lifetime measurements

- Development of methods for local hotspot analysis to quickly check critical interconnect segments without tool support

- SPICE-based migration modeling to explore stress evolution using standard IC design tools

EM-robust router for proactive EM consideration:

- EM-robust routing "by design" - robustness is ensured already during the routing step

- Reduction of EM-related repair effort after the verification

- Utilization of free routing resources to achieve improved EM robustness by:

- EM-driven routing order

- Optimized net topology

- Limitation of segment length

- Increased interconnect cross section (shift interconnects to higher metal layers)

- Reservoir insertion

- EM-optimized insertion of redundant vias

- Usually, those measures have to be applied to less than 10 % of all nets.

Other research topics:

- Analysis of circuit and layout designs to detect nets that are at danger of suffering EM degradation and to examine the impact of current profiles, current density and temperature profiles on EM

- Develpment of efficient current density and stress verification methods for interconnects and vias

- Investigation of novel technologies and proactive routing strategies for EM mitigation

- Implementation of an EM-robust routing flow with commercial design tools

- Assessment of thermal migration influence on the overall migration robustness of (AC) metal interconnects [FEM models on Github]

Textbook on EM-aware IC design

|

|

PhD theses on electromigration:

- S. Bigalke: Erhöhung der Elektromigrationsrobustheit in der Verdrahtung digitaler Schaltungen, 2019. [VDI-Verlag, SLUB]

- M. Thiele: Elektromigration und deren Berücksichtigung beim zukünftigen Layoutentwurf digitaler Schaltungen, 2017. [VDI-Verlag, SLUB]

Other EM-related publications:

- S. Rothe, J. Lienig, S. Muniswamy, M. Herklotz: "Experimental Characterization of Electromigration-Induced Stress Evolution in a 22nm-Technology" [pdf] in Proc. of the 2026 International Reliability Physics Symposium (IRPS), Tucson, USA, March 2026.

- K. Yahyaei, S. Rothe, M. Vawoo Dawood Naina, A. Roy, M. Shafkat, M. Khan, O. Sinanoglu, J. Lienig, J. Knechtel, N. Asadizanjani: "Lurking in the Shadows: Challenges for X-Ray Inspection to Uncover Electromigration-Based Hardware Trojans in Advanced Packaging," [pdf, IEEEXplore] in Proc. of the IEEE 2025 International Conference on Physical Assurance and Inspection of Electronics (PAINE 2025), Denver, USA, Oktober 2025. (Best Paper Nominee)

- S. Rothe, J. Lienig, S. S. Sapatnekar: "Temperature-aware Stress-based Migration Modeling in IC Design: Moving from Theory to Practice," [pdf, DOI] AEU - International Journal of Electronics and Communications, 155909, ISSN 1434-8411, June 2025.

- S. Rothe, J. Lienig, S. S. Sapatnekar: “Stress-based Electromigration Modeling in IC Design: Moving from Theory to Practice,” [pdf, IEEEXplore] in Proc. of the Int. Conf. on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD 2024), Volos, Greece, July 2024

- S. Rothe, J. Lienig "Combined Modeling of Electromigration, Thermal and Stress Migration in AC Interconnect Lines," in Proc. of the ACM 2023 Int. Symposium on Physical Design (ISPD'23), Virtual event, March 2023 [pdf, DOI, FEM-Modelle auf Github]

- S. Rothe, J. Lienig "Reliability by Design: Avoiding Migration-Induced Failure in IC Interconnects," [pdf, IEEEXplore] Proc. Symposium on Integrated Circuits and Systems Design (SBCCI), Brasil, Aug. 2022, DOI: 10.1109/SBCCI55532.2022.9893237

- J. Lienig, S. Rothe, M. Thiele, N. Rangarajan, M. Nabeel, H. Amrouch, O. Sinanoglu, J. Knechtel "Toward Security Closure in the Face of Reliability Effects," [pdf] Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. (ICCAD'21), Special Session, Munich, Nov. 2021, DOI: 10.1109/ICCAD51958.2021.9643447

- S. Bigalke, J. Lienig "Avoidance vs. Repair: New Approaches to Increasing Electromigration Robustness in VLSI Routing," [pdf] Integration, the VLSI Journal, vol. 65, ISSN 0167-9260, June 2020, DOI: 10.1016/j.vlsi.2020.04.009

- M. Thiele, S. Bigalke und J. Lienig, "Electromigration Analysis of VLSI Circuits Using the Finite Element Method," [pdf] In: VLSI-SoC: Opportunities and Challenges Beyond the Internet of Things. Hrsg. von M. Maniatakos, I. Elfadel, M. S. Reorda, F. Ugurdag, J. Monteiro und R. Reis. IFIP International Federation for Information Processing, Springer Nature Switzerland AG, 2019, DOI: 10.1007/978-3-030-15663-3_7

- S. Bigalke, J. Lienig, G. Jerke, J. Scheible and R. Jancke, "The Need and Opportunities of Electromigration-Aware Integrated Circuit Design," [pdf] In Proc. of 2018 Int. Conf. on Computer Aided Design (ICCAD), Nov. 2018, pp. 96:1--96:8, DOI: 10.1145/3240765.3265971

- S. Bigalke and J. Lienig, "FLUTE-EM: Electromigration-optimized net topology considering currents and mechanical stress," [pdf] In Proc. of 26th IFIP/IEEE Int. Conf. on Very Large Scale Integration (VLSI-SoC), Oct. 2018, pp. 225–230, DOI: 10.1109/VLSI-SoC.2018.8644965

- J. Lienig, M. Thiele "The Pressing Need for Electromigration-Aware Integrated Circuit Design," [pdf] Proc. of the ACM 2018 Int. Symposium on Physical Design (ISPD'18), Monterey, CA, pp. 144-151, March 2018.

- S. Bigalke, T. Casper, S. Schöps and J. Lienig, "Increasing EM Robustness of Placement and Routing Solutions based on Layout-Driven Discretization," [pdf] In Proc. of 2018 14th Conf. on Ph.D. Research in Microelectronics and Electronics (PRIME), Jul. 2018, pp. 89–92, DOI: 10.1109/PRIME.2018.8430323

- S. Bigalke and J. Lienig, "Load-aware redundant via insertion for electromigration avoidance," [pdf] In Proc. of 2016 ACM International Symposium on Physical Design (ISPD), Apr. 2016, pp. 99–106, DOI: 10.1145/2872334.2872355

- M. Thiele, S. Bigalke, J. Lienig, "Exploring the use of the finite element method for electromigration analysis in future physical design," [pdf] In Proc. of 2017 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), pp. 1–6, Oct. 2017, DOI: 10.1109/VLSI-SoC.2017.8203466

- M. Thiele, J. Lienig, "Vermeidung von Elektromigration durch kurze Segmentlängen im Layout digitaler Schaltungen," [pdf] Tagungsband Dresdner Arbeitstagung Schaltungs- und Systementwurf (DASS 2012), Fraunhofer Verlag, ISBN 978-3-8396-0404-5, pp. 52–56, May 2012.

- M. Thiele, J. Lienig, "Der Feind auf dem Chip – Elektromigration in digitalen Schaltungen," [pdf, elektroniknet.de] Elektronik, WEKA Fachmedien, Ausgabe 2, pp. 32–36, Feb. 2012.

- M. Thiele, J. Lienig, "Elektromigrationserscheinungen in zukünftigen digitalen Schaltungen," Tagungsband Dresdner Arbeitstagung Schaltungs- und Systementwurf (DASS 2011), Fraunhofer Verlag, ISBN 978-3-8396-0259-1 [Titel anhand dieser ISBN in Citavi-Projekt übernehmen] , pp. 30–35, May 2011.

- J. Lienig, "Introduction to Electromigration-Aware Physical Design," Invited Talk, [pdf] Proceedings of the International Symposium on Physical Design (ISPD'06), San Jose, CA, pp. 39–46, April 2006.

- G. Jerke, J. Lienig, J. Scheible, "Reliability-Driven Layout Decompaction for Electromigration Failure Avoidance in Complex Mixed-Signal IC Designs," [, slides] Proceedings of the Design Automation Conference (DAC'04), San Diego, CA, pp. 181–184, June 2004.

- G. Jerke, J. Lienig, "Hierarchical Current Density Verification in Arbitrarily Shaped Metallization Patterns of Analog Circuits," [pdf] IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 23, no. 1, pp. 80–90, Jan. 2004

- J. Lienig, G. Jerke, "Elektromigration -- eine neue Herausforderung beim Entwurf elektronischer Baugruppen," F&M Feinwerktechnik, Mikrotechnik, Mikroelektronik, Part I/Teil I: Ursachen und Beeinflussungsmöglichkeiten [pdf] : pp. 36–39, Oct. 2002, Part II/Teil II: Stromabhängige Verdrahtung von Leiterbahnen [pdf] : pp. 26–28, Jan./Feb. 2003, Part III/Teil III: Berechnung von Stromdichten [pdf] : pp. 12–15, March 2003.

- J. Lienig, G. Jerke, "Current-Driven Wire Planning for Electromigration Avoidance in Analog Circuits," [pdf, slides] Proceedings of the 8th Asia and South Pacific Design Automation Conference (ASP-DAC), Kitakyusyu, Japan, pp. 783–788, 2003.

Contact:

Dipl.-Ing. Susann Rothe

Dr.-Ing. Matthias Thiele

Prof. Dr.-Ing. habil. Jens Lienig

German version

German version