Forschungsschwerpunkt

Berücksichtigung und Vermeidung von Elektromigration beim Layoutentwurf

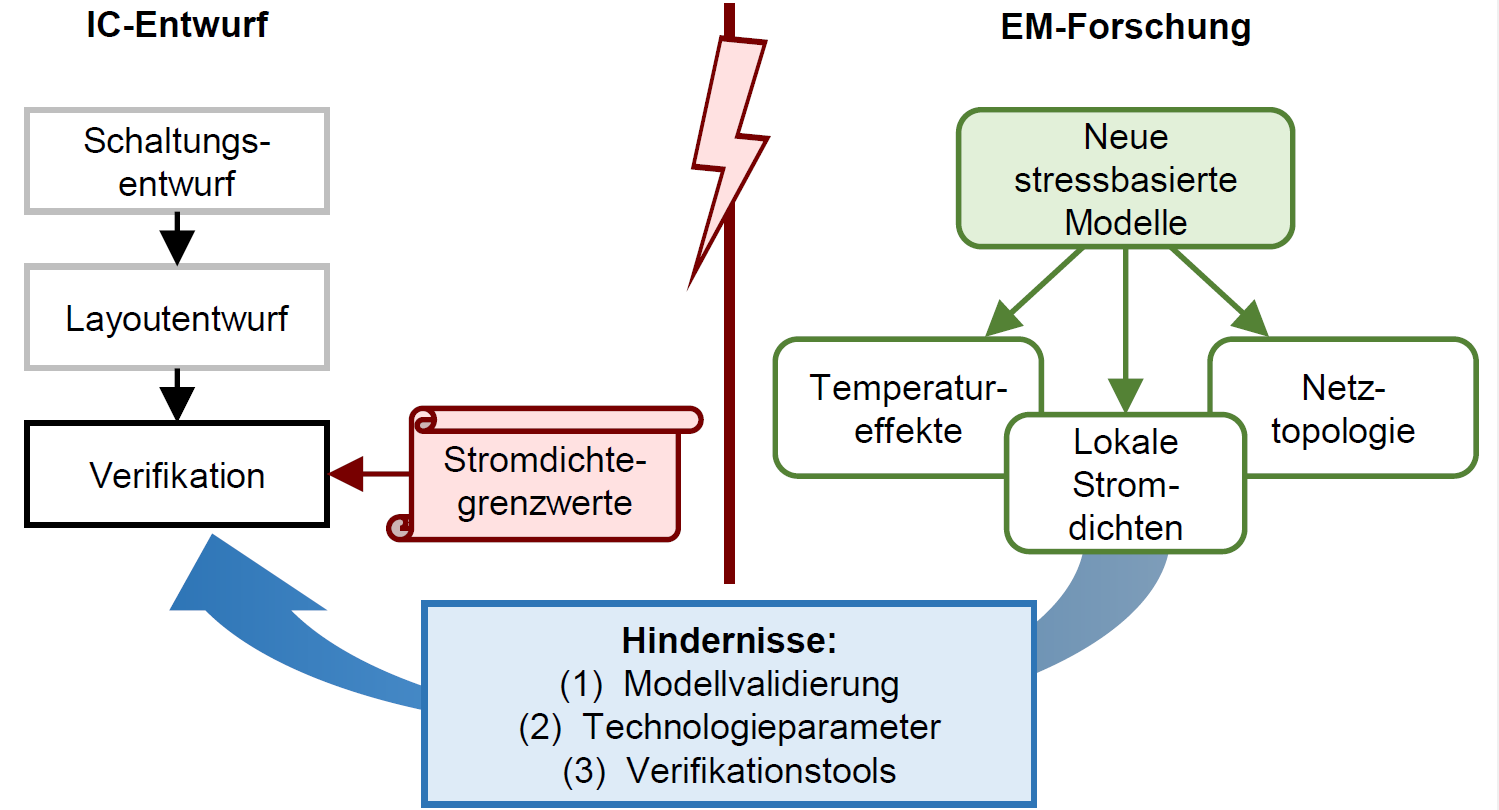

Elektromigration (EM) ist wegen sinkender Strukturgrößen zunehmend eine Gefahr für die Zuverlässigkeit integrierter Schaltkreise. Durch hohen Stromdichten kommt es zu einer Bewegung der Metallatome, wobei so entstehende Leerstellen ("Voids") zum Ausfall der Leiterbahn führen können. Etablierte Verifikationsmethoden prüfen das Layout nach seiner Erstellung auf die Einhaltung einer maximal zulässigen Stromdichte und damit auf Elektromigrationsrobustheit. Dieses Vorgehen stößt jedoch zunehmend an seine Grenzen. Ursache dafür sind einmal die zugrundeliegenden Stromdichtemodelle, welche die physikalischen Zusammenhänge nur unzureichend darstellen und somit hohe Sicherheitsfaktoren nötig machen. Auch steigt durch die zunehmende Anzahl EM-gefährdeter Netze der Korrekturaufwand im Anschluss an die Verifikation auf ein nicht mehr handhabbares Maß.

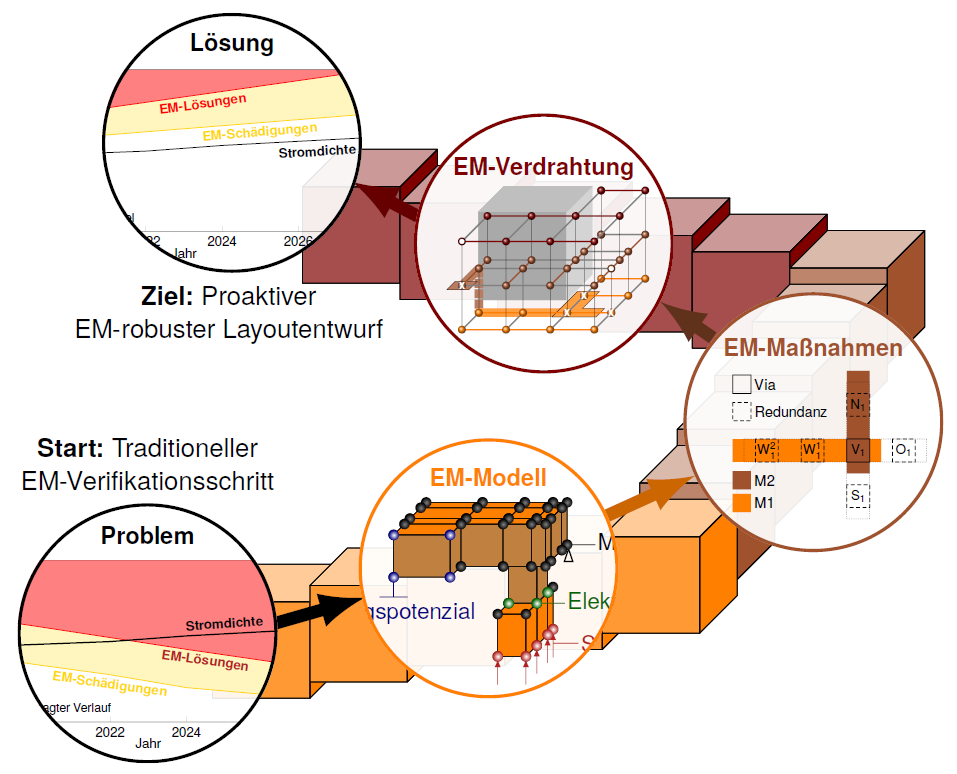

Um auch in zukünftigen Technologien den migrationsrobusten Schaltkreis-Entwurf zu gewährleisten, wird am IFTE an Methoden gearbeitet, welche neue, stressbasierte Migrationsmodelle in die praktische Anwendung überführen. Diese Modelle berechnen die Stessentwicklung (als Maß für die Migrationsgefährdung) in Leiterbahnen unter Berücksichtigung der lokalen Stromdichteverteilung und der Netztopologie. Damit überwinden sie die pessimistische Migrationsbewertung, welche den etablierten Stromdichtemodellen zueigen ist.

Außerdem entstand am IFTE ein innovativer proaktiver Verdrahtungsansatz, welcher die Migrationsrobustheit bereits während der Layouterstellung berücksichtigt. Damit verringert sich der Korrekturaufwand nach der Verifikation deutlich.

Praktische Anwendbarkeit der neuen Stressmodelle:

- Entwicklung und Test von Verfahren zur Technologiecharakterisierung für die Stressmodelle - basierend auf etablierten Lebensdauermessungen

- Entwicklung von Methoden zur lokalen Hotspot-Analyse, um schnell und ohne Tool-Unterstützung kritische Leiterbahnsegmente zu überprüfen

- SPICE-basierte Migrationsmodellierung, um die Stressentwicklung mit etablierten IC-Design-Tools zu untersuchen

EM-robuster Verdrahter zur proaktiven EM-Berücksichtigung:

- Elektromigrationsrobuste Verdrahtung "by Design", also Robustheit bereits bei der Verdrahtung

- Reduktion des Reparaturen von EM-Problemen nach der Verifikation

- Nutzung von verfügbaren Verdrahtungsressourcen zur Steigerung der EM-Robustheit durch:

- Verdrahtung in der Reihenfolge des EM-Risikos

- Optimierte Netztopologie

- Begrenzung der Segmentlängen

- Anpassung des Leiterbahnquerschnitts

- Einfügen von Reservoiren

- EM-optimiertes Einsetzen von redundanten Vias

- In der Regel genügt die Anwendung für maximal 10 Prozent der zu verdrahtenden Netze

Weitere Forschungsthemen:

- Schaltungs- und Layoutanalyse zur Ermittlung EM-gefährdeter Netze und Untersuchung des Einflusses verschiedener Stromarten, Stromdichten und Temperaturprofile auf die Elektromigration

- Entwicklung von effektiven Stromdichte- und Stress-Verifikationsmethoden für Leiterbahnen und Vias unterschiedlichster Geometrien

- Untersuchung neuartiger Technologien und proaktiver Verdrahtungsmethoden zur Vermeidung von EM-Erscheinungen

- Implementierung der EM-robusten Verdrahtung in kommerziellen EDA-Tools

- Bewertung des Einflusses der Thermomigration auf die Migrationsrobustheit von (AC)-Leiterbahnen [FEM-Modelle auf Github]

Fachbuch zum EM-robusten Schaltkreisentwurf:

|

|

Dissertationen zur Elektromigration:

- S. Bigalke: Erhöhung der Elektromigrationsrobustheit in der Verdrahtung digitaler Schaltungen, 2019. [VDI-Verlag, SLUB]

- M. Thiele: Elektromigration und deren Berücksichtigung beim zukünftigen Layoutentwurf digitaler Schaltungen, 2017. [VDI-Verlag, SLUB]

Weitere Veröffentlichungen (Auswahl):

- S. Rothe, J. Lienig, S. Muniswamy, M. Herklotz: "Experimental Characterization of Electromigration-Induced Stress Evolution in a 22nm-Technology" [pdf] in Proc. of the 2026 International Reliability Physics Symposium (IRPS), Tucson, USA, März 2026.

- K. Yahyaei, S. Rothe, M. Vawoo Dawood Naina, A. Roy, M. Shafkat, M. Khan, O. Sinanoglu, J. Lienig, J. Knechtel, N. Asadizanjani: "Lurking in the Shadows: Challenges for X-Ray Inspection to Uncover Electromigration-Based Hardware Trojans in Advanced Packaging," [pdf, IEEEXplore] in Proc. of the IEEE 2025 International Conference on Physical Assurance and Inspection of Electronics (PAINE 2025), Denver, USA, Oktober 2025. (Best Paper Nominee)

- S. Rothe, J. Lienig, S. S. Sapatnekar: "Temperature-aware Stress-based Migration Modeling in IC Design: Moving from Theory to Practice," [pdf, DOI] AEU - International Journal of Electronics and Communications, 155909, ISSN 1434-8411, June 2025.

- S. Rothe, J. Lienig, S. S. Sapatnekar: “Stress-based Electromigration Modeling in IC Design: Moving from Theory to Practice,” [pdf, IEEEXplore] in Proc. of the Int. Conf. on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD 2024), Volos, Greece, July 2024

- S. Rothe, J. Lienig "Combined Modeling of Electromigration, Thermal and Stress Migration in AC Interconnect Lines," in Proc. of the ACM 2023 Int. Symposium on Physical Design (ISPD'23), Virtuelle Veranstaltung, März 2023 [pdf, DOI, FEM-Modelle auf Github]

- S. Rothe, J. Lienig "Reliability by Design: Avoiding Migration-Induced Failure in IC Interconnects," [pdf, IEEEXplore] Proc. Symposium on Integrated Circuits and Systems Design (SBCCI), Brasilien, Aug. 2022, DOI: 10.1109/SBCCI55532.2022.9893237

- J. Lienig, S. Rothe, M. Thiele, N. Rangarajan, M. Nabeel, H. Amrouch, O. Sinanoglu, J. Knechtel "Toward Security Closure in the Face of Reliability Effects," [pdf] Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. (ICCAD'21), Special Session, Munich, Nov. 2021, DOI: 10.1109/ICCAD51958.2021.9643447

- S. Bigalke, J. Lienig "Avoidance vs. Repair: New Approaches to Increasing Electromigration Robustness in VLSI Routing," [pdf] Integration, the VLSI Journal, vol. 65, ISSN 0167-9260, June 2020, DOI: 10.1016/j.vlsi.2020.04.009

- M. Thiele, S. Bigalke und J. Lienig, "Electromigration Analysis of VLSI Circuits Using the Finite Element Method," [pdf] In: VLSI-SoC: Opportunities and Challenges Beyond the Internet of Things. Hrsg. von M. Maniatakos, I. Elfadel, M. S. Reorda, F. Ugurdag, J. Monteiro und R. Reis. IFIP International Federation for Information Processing, Springer Nature Switzerland AG, 2019, DOI: 10.1007/978-3-030-15663-3_7

- S. Bigalke, J. Lienig, G. Jerke, J. Scheible and R. Jancke, "The Need and Opportunities of Electromigration-Aware Integrated Circuit Design," [pdf] In Proc. of 2018 Int. Conf. on Computer Aided Design (ICCAD), Nov. 2018, pp. 96:1--96:8, DOI: 10.1145/3240765.3265971

- S. Bigalke and J. Lienig, "FLUTE-EM: Electromigration-optimized net topology considering currents and mechanical stress," [pdf] In Proc. of 26th IFIP/IEEE Int. Conf. on Very Large Scale Integration (VLSI-SoC), Oct. 2018, pp. 225–230, DOI: 10.1109/VLSI-SoC.2018.8644965

- J. Lienig, M. Thiele "The Pressing Need for Electromigration-Aware Integrated Circuit Design," [pdf] Proc. of the ACM 2018 Int. Symposium on Physical Design (ISPD'18), Monterey, CA, pp. 144-151, March 2018.

- S. Bigalke, T. Casper, S. Schöps and J. Lienig, "Increasing EM Robustness of Placement and Routing Solutions based on Layout-Driven Discretization," [pdf] In Proc. of 2018 14th Conf. on Ph.D. Research in Microelectronics and Electronics (PRIME), Jul. 2018, pp. 89–92, DOI: 10.1109/PRIME.2018.8430323

- S. Bigalke and J. Lienig, "Load-aware redundant via insertion for electromigration avoidance," [pdf] In Proc. of 2016 ACM International Symposium on Physical Design (ISPD), Apr. 2016, pp. 99–106, DOI: 10.1145/2872334.2872355

- M. Thiele, S. Bigalke, J. Lienig, "Exploring the use of the finite element method for electromigration analysis in future physical design," [pdf] In Proc. of 2017 IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), pp. 1–6, Oct. 2017, DOI: 10.1109/VLSI-SoC.2017.8203466

- M. Thiele, J. Lienig, "Vermeidung von Elektromigration durch kurze Segmentlängen im Layout digitaler Schaltungen," [pdf] Tagungsband Dresdner Arbeitstagung Schaltungs- und Systementwurf (DASS 2012), Fraunhofer Verlag, ISBN 978-3-8396-0404-5, pp. 52–56, May 2012.

- M. Thiele, J. Lienig, "Der Feind auf dem Chip – Elektromigration in digitalen Schaltungen," [pdf, elektroniknet.de] Elektronik, WEKA Fachmedien, Ausgabe 2, pp. 32–36, Feb. 2012.

- M. Thiele, J. Lienig, "Elektromigrationserscheinungen in zukünftigen digitalen Schaltungen," Tagungsband Dresdner Arbeitstagung Schaltungs- und Systementwurf (DASS 2011), Fraunhofer Verlag, ISBN 978-3-8396-0259-1 [Titel anhand dieser ISBN in Citavi-Projekt übernehmen] , pp. 30–35, May 2011.

- J. Lienig, "Introduction to Electromigration-Aware Physical Design," Invited Talk, [pdf] Proceedings of the International Symposium on Physical Design (ISPD'06), San Jose, CA, pp. 39–46, April 2006.

- G. Jerke, J. Lienig, J. Scheible, "Reliability-Driven Layout Decompaction for Electromigration Failure Avoidance in Complex Mixed-Signal IC Designs," [, slides] Proceedings of the Design Automation Conference (DAC'04), San Diego, CA, pp. 181–184, June 2004.

- G. Jerke, J. Lienig, "Hierarchical Current Density Verification in Arbitrarily Shaped Metallization Patterns of Analog Circuits," [pdf] IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 23, no. 1, pp. 80–90, Jan. 2004

- J. Lienig, G. Jerke, "Elektromigration -- eine neue Herausforderung beim Entwurf elektronischer Baugruppen," F&M Feinwerktechnik, Mikrotechnik, Mikroelektronik, Part I/Teil I: Ursachen und Beeinflussungsmöglichkeiten [pdf] : pp. 36–39, Oct. 2002, Part II/Teil II: Stromabhängige Verdrahtung von Leiterbahnen [pdf] : pp. 26–28, Jan./Feb. 2003, Part III/Teil III: Berechnung von Stromdichten [pdf] : pp. 12–15, March 2003.

- J. Lienig, G. Jerke, "Current-Driven Wire Planning for Electromigration Avoidance in Analog Circuits," [pdf, slides] Proceedings of the 8th Asia and South Pacific Design Automation Conference (ASP-DAC), Kitakyusyu, Japan, pp. 783–788, 2003.

Ansprechpersonen:

Dipl.-Ing. Susann Rothe

Dr.-Ing. Matthias Thiele

Prof. Dr.-Ing. habil. Jens Lienig

Englische Version

Englische Version