Research Focus

3D Physical Design Algorithms and Data Structures

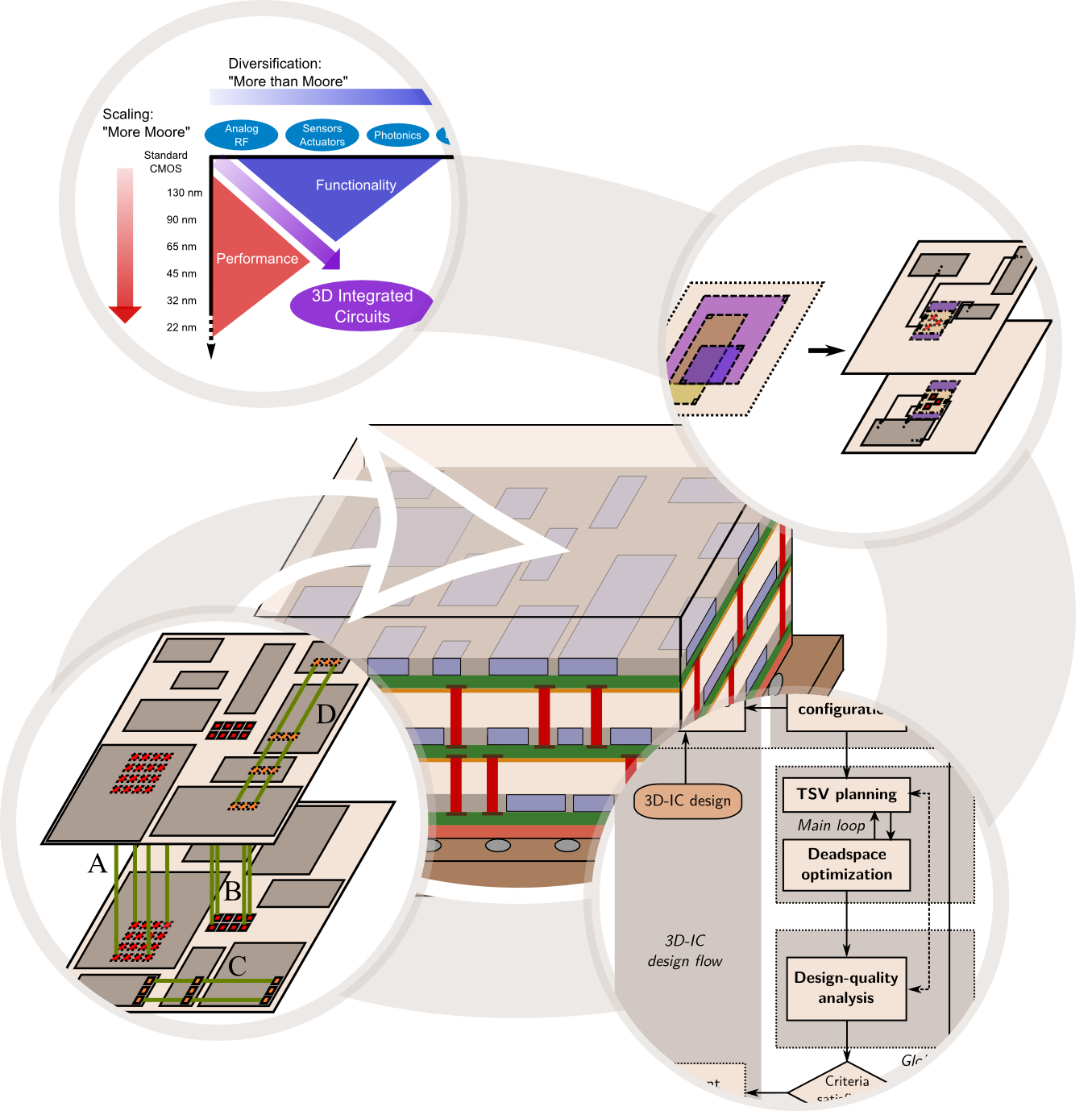

Three-dimensional integrated circuits (3D-ICs) make use of advanced manufacturing methodologies such that multiple active chips can be stacked. Integrating chips in the third dimension allows for increased packing densities, shorter interconnects and heterogeneous systems. However, the commercial application of 3D-ICs is still notably impeded by design and manufacturing challenges.

Research Approaches:

- New approaches for physical design optimization and modeling of 3D-ICs under consideration of vertical interconnects, the through-silicon vias (TSVs)

- Representation of three-dimensional circuits in suitable data structures

- Optimized reuse of classical 2D-IP-blocks for 3D-IC design

Selected Results:

- A new design methodology for assembling 2D-IP-blocks in 3D-ICs

- A multiobjective layout-optimization approach for guided TSV planning

- An extended data structure for optimized planning of inter-die and intra-die connects in 3D-ICs

- A new data structure, enabling floorplanning of complex-shaped rectilinear 2D and 3D blocks

- A methodology for applied solution-space investigations of data structures

For related publications, please see here.

Downloads:

Corblivar, a simulated-annealing-based floorplanning suite for 3D ICs, with special emphasis on planning of massively-parallel interconnects and fast thermal analysis

Please consider this software experimental

Corblivar, latest version on GitHub

HotSpot, latest version on GitHub

Investigation tool for layout representations; includes implementation of 3D Moving Block Sequence (3D-MBS)

Please consider this software experimental (Snapshot 2012-05-21):

Documentation (user manual)

Application programming interface (API)

Source code package (Python 2.6)

THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

German version

German version